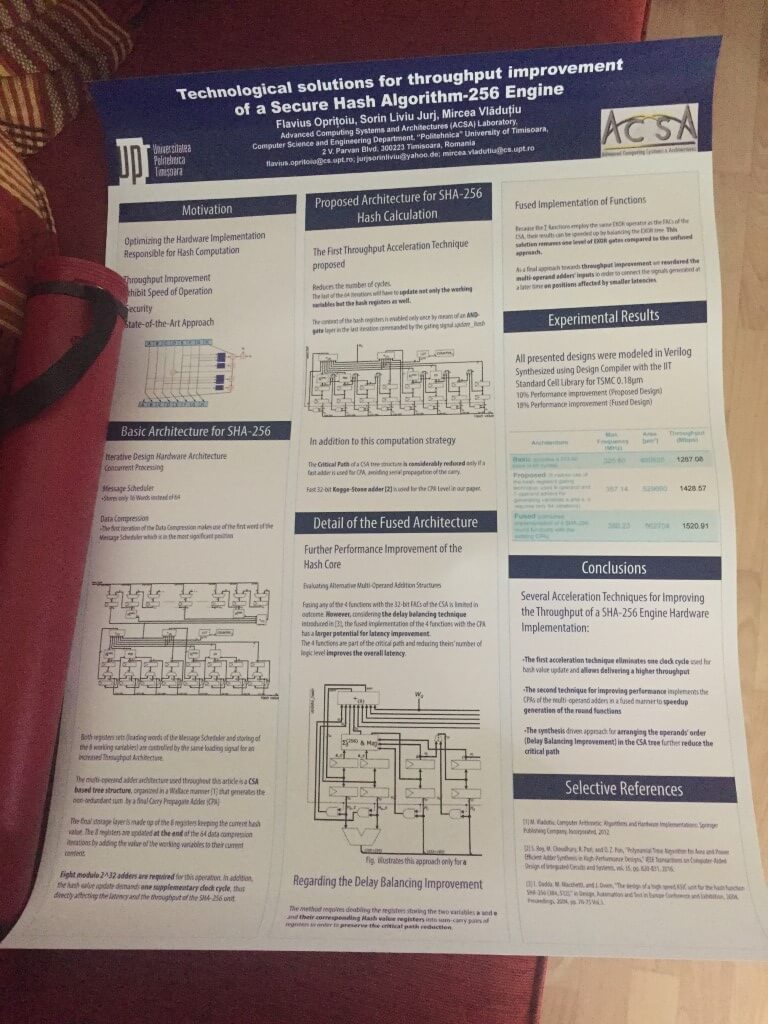

Am Ende Oktober 2017 bin ich nach Constanța, Rumänien geflogen um an 2017 IEEE 23. Internationales Symposium für Design und Technologie in der Elektronikverpackung (SIITME) teilzunehmen wo ich den Forschungsartikel „Technological solutions for throughput improvement of a Secure Hash Algorithm-256 engine“ (Technologische Lösungen zur Durchsatzverbesserung einer Secure Hash Algorithm-256-Engine) als Co-Autor präsentiert habe. Abstrakt: Dieser Artikel beschreibt eine Reihe von Techniken zum Verbessern der Leistung einer Secure Hash Algorithm 256 (SHA-256) Hardwareimplementierung. Die vorgeschlagene Lösung reduziert die Latenzzeit, die zum Aktualisieren der Zwischen-Hash-Werte anfällt, und beruht auf der Verwendung kombinatorischer Baumstrukturen von CSAs, die in einer Wallace-Baum-Art für die Addition mehrerer Operanden miteinander verbunden sind. Darüber hinaus untersucht das Papier die durchgängige Verbesserung, die durch eine kombinierte Implementierung von binären Addierern der Architektur mit den runden Funktionen bereitgestellt wird, die von dem Hash-Berechnungsprozess verwendet werden. Die vorgeschlagenen Beschleunigungstechniken können an die anderen Mitglieder der SHA-2-Familie von Algorithmen angepasst werden. Die Architektur stellt eine Fallstudie für Hardware-Optimierung dar, die auf verschiedenen kombinatorischen Strukturen für die binäre Addition und den Effekt der Carry-Propagate-Schicht auf die Gesamtleistung basiert. Die Syntheseergebnisse der vorgeschlagenen Designs werden als Unterstützung für die in dieser Arbeit präsentierte Leistungsanalyse bereitgestellt.

Abstrakt: Dieser Artikel beschreibt eine Reihe von Techniken zum Verbessern der Leistung einer Secure Hash Algorithm 256 (SHA-256) Hardwareimplementierung. Die vorgeschlagene Lösung reduziert die Latenzzeit, die zum Aktualisieren der Zwischen-Hash-Werte anfällt, und beruht auf der Verwendung kombinatorischer Baumstrukturen von CSAs, die in einer Wallace-Baum-Art für die Addition mehrerer Operanden miteinander verbunden sind. Darüber hinaus untersucht das Papier die durchgängige Verbesserung, die durch eine kombinierte Implementierung von binären Addierern der Architektur mit den runden Funktionen bereitgestellt wird, die von dem Hash-Berechnungsprozess verwendet werden. Die vorgeschlagenen Beschleunigungstechniken können an die anderen Mitglieder der SHA-2-Familie von Algorithmen angepasst werden. Die Architektur stellt eine Fallstudie für Hardware-Optimierung dar, die auf verschiedenen kombinatorischen Strukturen für die binäre Addition und den Effekt der Carry-Propagate-Schicht auf die Gesamtleistung basiert. Die Syntheseergebnisse der vorgeschlagenen Designs werden als Unterstützung für die in dieser Arbeit präsentierte Leistungsanalyse bereitgestellt.

Sie können den Artikel hier lesen: http://ieeexplore.ieee.org/document/8259881/

Neueste Kommentare